随着电子设备日益复杂和集成化,电磁兼容性已成为集成电路设计中不可或缺的关键因素。电磁兼容性测试旨在确保IC在预期电磁环境中能正常工作,同时不对其他设备产生不可接受的干扰。本文将系统阐述IC的EMC主要测试标准,并探讨其在设计阶段的核心考量。

一、集成电路EMC主要测试标准

国际电工委员会、国际标准化组织及各国标准化机构制定了一系列针对IC的EMC测试标准,其中最具影响力的包括:

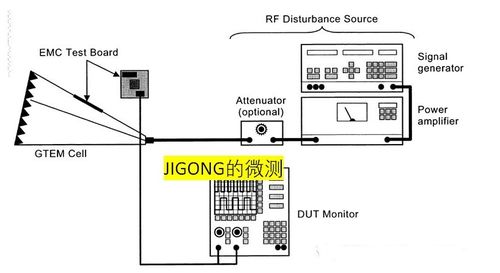

1. IEC 61967系列标准:专门用于测量IC在150 kHz至1 GHz频率范围内产生的传导和辐射发射。该系列标准详细规定了测试方法,如使用TEM小室、表面扫描法等测量辐射发射,以及使用1Ω/150Ω直接耦合法测量传导发射。

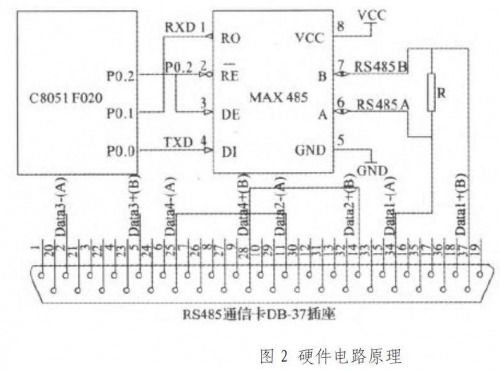

2. IEC 62132系列标准:侧重于IC的电磁抗扰度测试,评估IC在遭受射频干扰、静电放电、电快速瞬变等干扰时的性能。常用方法包括直接射频功率注入、大电流注入等。

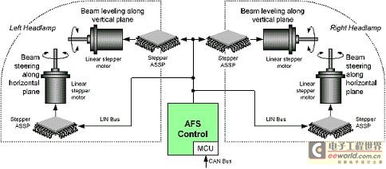

3. 汽车电子标准:如ISO 11452-4(大电流注入)和ISO 10605(静电放电),对车规级IC提出了更严苛的要求,以确保在恶劣电磁环境下的可靠性。

4. JEDEC标准:如JESD22-A114(ESD)和JESD22-A115(闩锁效应),虽不专为EMC设计,但与IC的抗干扰能力密切相关。

这些标准为IC的EMC性能提供了统一的测试基准和评估方法,是产品认证和市场准入的重要依据。

二、集成电路设计中的EMC考量

要在芯片层面实现良好的EMC性能,必须在设计阶段就融入EMC思维,而非仅依赖后期测试与整改。关键设计策略包括:

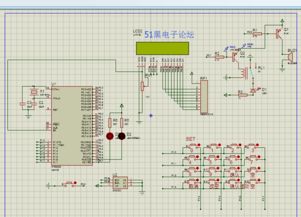

- 电源完整性设计:采用低阻抗的电源分配网络,合理使用去耦电容和电源层,以抑制电源噪声传播。片上稳压器、电源域隔离技术能有效减少噪声耦合。

- 信号完整性管理:对高速信号线实施阻抗匹配、差分布线,减少信号反射和串扰。时钟电路应特别关注,采用展频时钟技术可降低峰值辐射。

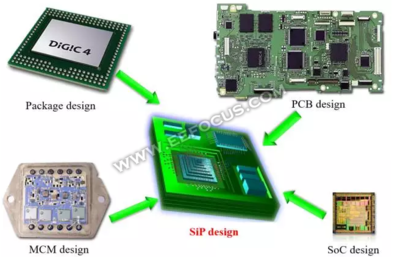

- 封装与引脚规划:优化封装结构,如使用接地环、屏蔽罩或倒装芯片技术以增强屏蔽效果。合理安排电源、接地及I/O引脚,减少回路面积,降低天线效应。

- 片上保护电路:集成ESD保护二极管、瞬态电压抑制器及射频滤波结构,提升芯片对瞬态干扰的耐受能力。

- 软件与固件策略:设计看门狗定时器、错误检测与纠正机制,使芯片在受到干扰后能自动恢复,增强系统级鲁棒性。

三、测试与设计的协同

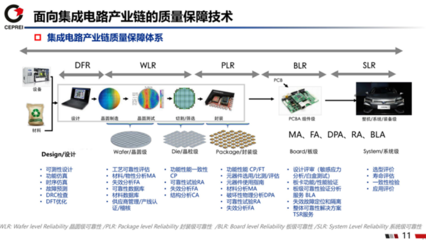

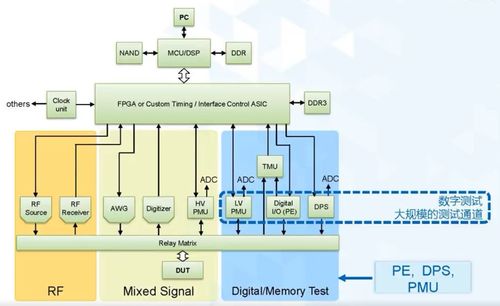

EMC测试不仅是验证手段,更是设计迭代的反馈源。通过测试可以识别噪声源和敏感路径,进而指导版图优化、电路调整。随着系统级封装和三维集成技术的发展,芯片与封装的协同设计对EMC的影响愈发显著,需要从系统视角进行整体优化。

在集成电路迈向更高速度、更低功耗和更小尺寸的进程中,EMC已成为与性能、成本并列的核心设计约束。深入理解EMC测试标准,并在设计初期系统性地实施EMC设计规则,不仅能缩短产品开发周期、降低合规成本,更能从根本上提升产品的可靠性和市场竞争力。随着5G、物联网和自动驾驶等应用的普及,对IC的EMC要求将愈加严格,推动测试标准与设计方法不断创新。