在集成电路(IC)发展的宏大叙事中,有一条定律曾长期占据主导地位——摩尔定律。它预言集成电路上可容纳的晶体管数量每隔约两年便会增加一倍,性能也随之提升。数十年来,这一定律如同一盏明灯,指引着半导体产业沿着“制程微缩”的单一轨道高速前行,从微米级一路狂奔至如今的纳米级。在这场以“更小、更快、更省电”为核心的技术赛跑中,几乎所有目光都聚焦在芯片本身的晶体管密度上,而一种名为“系统级封装”(System in Package, SiP)的技术,尽管其概念早已存在,却长期被遗忘在产业发展的角落,鲜少受到主流关注。

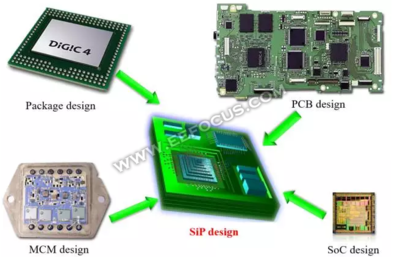

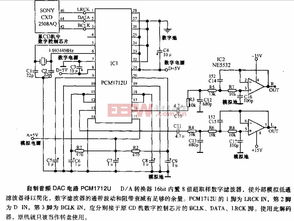

SiP并非新生事物。早在上世纪七八十年代,多芯片模块(MCM)等封装技术便已萌芽,可被视为SiP的雏形。它的核心理念是将多个具有不同功能的芯片(如处理器、存储器、传感器、无源元件等)通过先进的封装技术集成在一个封装体内,形成一个功能完整的系统或子系统。在摩尔定律的黄金时代,通过制程升级来集成更多功能、提升性能的路径清晰且高效。芯片设计者更倾向于追求单颗芯片上系统级(SoC, System on Chip)的集成,因为这在当时被认为是性能最优、成本最低的解决方案。相比之下,SiP技术显得复杂、成本较高,且在当时封装技术有限的条件下,其性能与可靠性优势并不突出,因此长期停留在军事、航天等少数对尺寸、重量有极端要求,且不计成本的特殊领域。

技术发展的轨迹并非永远直线向前。进入21世纪第二个十年后,摩尔定律的延续性开始面临前所未有的严峻挑战。物理极限、量子效应、惊人的研发与制造成本(“经济摩尔定律”的失效)如同三座大山,使得制程微缩的步伐明显放缓,每一步进阶都变得异常艰难且昂贵。单纯依靠晶体管尺寸缩小来提升系统性能的“免费午餐”时代已然终结。与此现代电子产品的需求却日益复杂多元:5G通信、人工智能、物联网、可穿戴设备等不仅要求极高的处理性能,还迫切需求异质集成(将不同工艺节点、不同材料的芯片,如数字CMOS、模拟RF、硅光芯片、MEMS传感器等整合在一起)、微型化、低功耗以及更短的上市时间。

正是在这样的产业变局下,曾被遗忘的SiP技术迎来了历史性的回归与复兴。人们突然发现,当“从下而上”的芯片级微缩遇到瓶颈时,“从上而下”的封装级系统集成提供了一条极具吸引力的替代路径。SiP的核心优势恰恰能应对新时代的挑战:

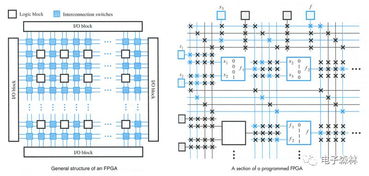

- 异质集成能力:SiP允许将采用不同工艺技术(如28nm逻辑芯片、55nm射频芯片、MEMS、GaN功率器件等)制造的芯片封装在一起,实现最优化的功能组合,这是单一工艺的SoC难以企及的。

- 缩短开发周期与降低成本:设计一颗包含所有功能的先进制程SoC,其研发投入动辄数亿美元,周期长达数年。而SiP可以复用成熟的芯片(称为“芯粒”或Chiplet),通过封装集成快速构成系统,大大降低了设计复杂性和风险,加速产品上市。

- 超越摩尔(More than Moore):SiP是实现“超越摩尔”定律的典范。它不再单纯追求晶体管密度的提升,而是通过系统级的封装创新,在提升整体性能、增加功能多样性的有效控制了成本与功耗。

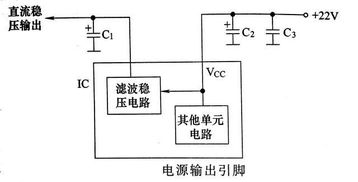

- 满足微型化需求:对于智能手机、TWS耳机、智能手表等空间极其受限的设备,SiP可以将多个芯片堆叠(3D SiP)起来,显著节省PCB主板面积,是实现设备轻薄化的关键技术。

如今,SiP已从昔日的边缘技术跃升为集成电路设计领域的核心焦点之一。它与芯粒(Chiplet)技术协同,共同构成了先进封装生态系统的两大支柱。从苹果Apple Watch中的S系列芯片,到高端手机中的射频前端模块,再到高性能计算中的2.5D/3D集成方案,SiP的身影无处不在。各大半导体巨头(如台积电的3DFabric、英特尔的Foveros、三星的X-Cube)和顶级封测厂都在重金投入相关研发。

可以说,SiP的“被遗忘”与“再回归”,深刻反映了半导体产业技术驱动力的变迁。它因摩尔定律的强势而隐没,又因摩尔定律的式微而闪耀。这不仅是封装技术的胜利,更是系统设计思维的胜利。随着硅通孔(TSV)、扇出型(Fan-Out)、混合键合(Hybrid Bonding)等技术的不断成熟,SiP将继续与先进制程、芯片架构创新深度融合,推动集成电路设计从“以芯片为中心”向“以系统为中心”进行范式转移,在摩尔定律的“后时代”开辟出更为广阔的性能与创新疆域。