自1958年杰克·基尔比发明第一块集成电路至今,这项技术已走过波澜壮阔的一甲子。六十余年间,方寸之间的芯片,从寥寥数个晶体管到如今百亿级集成,不仅见证了半导体产业的腾飞,更成为驱动人类社会数字化转型的核心引擎。在这段跨越时代的旅程中,集成电路设计——作为连接抽象算法与物理实体的关键桥梁,其理念、方法与工具的演进,本身便是一部浓缩的科技史诗。

一、 起源与萌芽:从手工布局到EDA雏形

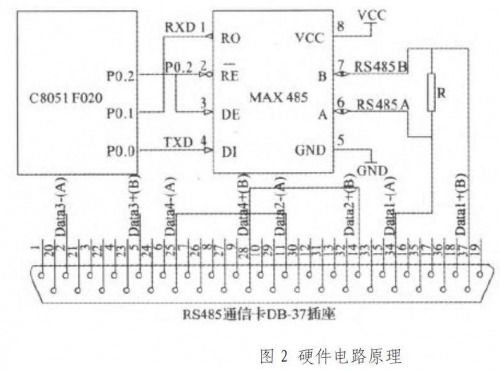

集成电路设计的开端,与工艺水平紧密相连。早期,设计者们如同绘制城市地图,在方格纸上用手工绘制每个晶体管和连线的几何图形,工作繁复且极易出错。随着电路规模扩大,计算机辅助设计(CAD)技术应运而生。70年代,以版图编辑、逻辑模拟和电路仿真为代表的初期电子设计自动化(EDA)工具开始出现,将设计师从大量重复劳动中解放出来,标志着设计方法学的一次革命。

二、 黄金年代:抽象层级提升与设计方法学革新

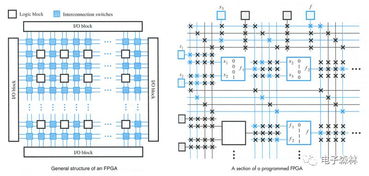

进入80年代,超大规模集成电路(VLSI)时代来临。摩尔定律的持续生效,使得芯片复杂度呈指数级增长。传统的晶体管级设计已无法应对。这一时期,设计抽象层级被显著提升:从寄存器传输级(RTL)描述硬件功能,到使用硬件描述语言(如VHDL、Verilog),设计焦点从“几何图形”转向“功能与结构”。同步诞生的逻辑综合技术,能够自动将RTL代码转换为门级网表,极大提升了设计效率和规范性。标准单元库和基于单元的设计流程成为主流,奠定了现代数字集成电路设计的基石。

三、 SoC时代:系统级集成与IP复用哲学

90年代末至21世纪初,单个芯片上集成整个系统成为可能,系统级芯片(SoC)登上舞台。设计复杂度从千万门级跃升至亿门级,挑战空前。单纯的逻辑设计已不够,需要处理处理器、存储器、模拟模块、各类接口的协同。由此,“设计复用”理念深入人心。预先设计、经过验证的集成电路知识产权核(IP Core)如同“乐高积木”,被广泛用于快速构建复杂SoC。设计重心进一步上移至系统架构定义、软硬件协同设计以及验证——验证工作量常常占据整个设计周期的70%以上。

四、 后摩尔定律时代:多维拓展与软硬件协同新范式

当工艺节点进入纳米尺度后,功耗、可靠性、制造成本等挑战日益严峻。延续摩尔定律的“缩放”收益递减,集成电路设计进入“后摩尔时代”。设计创新向多个维度拓展:

- 架构创新:面对数据洪流与AI计算需求,通用CPU架构不再一枝独秀。领域专用架构(DSA),如GPU、NPU、各种加速器IP,通过软硬件深度协同,在能效比上实现数量级提升。

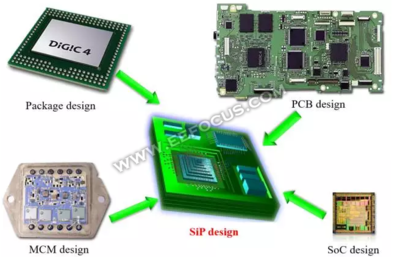

- 先进封装与异构集成:通过2.5D/3D堆叠、芯粒(Chiplet)等技术,将不同工艺、不同功能的芯片粒集成在一个封装内,成为延续系统性能提升的关键路径。这要求设计范畴从单芯片扩展到跨芯片互连、协同设计与系统级封装。

- 设计工具智能化:借助人工智能与机器学习,EDA工具正在设计空间探索、布局布线、验证测试等环节实现智能化突破,以应对千亿晶体管时代的设计复杂度。

五、 未来展望:面向应用与跨学科融合

展望下一个甲子,集成电路设计将继续朝着更高抽象层级、更强智能化和更紧密的跨学科融合方向发展。

- 系统-应用共同优化:设计将更早、更深入地与终端应用(如自动驾驶、生物医疗、元宇宙)结合,实现从应用需求到芯片架构的垂直优化。

- 计算-存储-通信融合:打破“内存墙”和“带宽墙”,探索存算一体、光计算等新计算范式下的设计方法学。

- 安全与可信设计:硬件安全、隐私保护将成为芯片设计初期就必须考虑的基石要素。

****

六十载光阴,集成电路设计从一门精密的“手艺”,演进为一门复杂的、高度自动化的“系统科学”。方寸硅片之上,凝聚的不仅是数十亿晶体管,更是人类智慧的层层抽象与无限创造力。站在新起点,面对日益复杂的应用场景与基础技术挑战,集成电路设计将继续作为创新的核心驱动力,在更微观的尺度与更宏大的系统层面上,谱写下一个时代的篇章。