随着半导体工艺节点不断向纳米尺度乃至更小尺度演进,集成电路设计面临着前所未有的挑战。传统的设计方法学在应对工艺偏差、参数波动、可靠性退化以及日益复杂的系统集成时,已显露出其局限性。因此,一种以“成功率”和“可靠性”为核心驱动力的新型集成电路设计方法学应运而生,成为确保先进芯片性能、良率和长期稳定运行的关键。

一、纳米尺度设计的新挑战

在纳米尺度下,器件的物理特性发生了显著变化。工艺波动(如线宽、掺杂浓度、氧化层厚度的随机变化)不再是可忽略的次要因素,而是成为影响电路性能与功能正确性的主导因素之一。晶体管栅氧层变薄、电流密度增大,使得电迁移、负偏置温度不稳定性(NBTI)、热载流子注入(HCI)等可靠性退化机制愈发突出。这些因素共同导致设计结果的确定性降低,设计“首次成功”的难度急剧增加,芯片在生命周期内的失效风险上升。

二、方法学的核心驱动力:成功率与可靠性

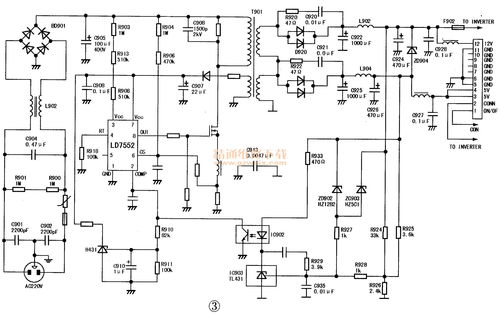

- 成功率驱动:这里的“成功率”主要指“首次流片成功率”和“设计收敛效率”。它强调在设计阶段就充分预测并规避由制造不确定性带来的风险。其核心在于将制造端的工艺波动信息,提前建模并整合到设计流程中,通过统计静态时序分析(SSTA)、工艺角压缩、片上工艺监测电路(PVT Sensor)等技术,使设计能够在广泛的工艺、电压、温度(PVT)变化范围内正常工作,从而一次性实现设计目标,避免昂贵且耗时的多次流片迭代。

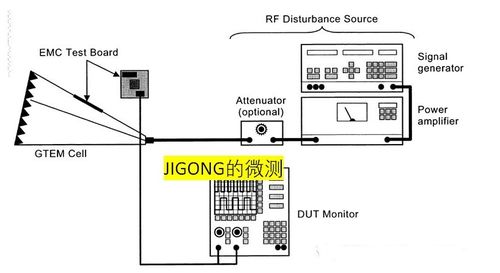

- 可靠性驱动:可靠性关注芯片在整个预期寿命内的功能完好性。纳米尺度下,可靠性必须从“事后补救”转变为“事前预防”和“事中管理”。这要求在设计阶段就进行可靠性建模与仿真(如预测NBTI导致的阈值电压漂移)、采用抗老化设计技术(如自适应体偏置、冗余设计)、集成在线健康监测与自修复机制。可靠性驱动设计确保芯片不仅在出厂时合格,更能在其使用寿命内持续稳定工作,满足汽车电子、工业控制、数据中心等关键应用领域的严苛要求。

三、关键技术与方法

- 统计设计与仿真:摒弃传统的固定角(Corner)分析,采用基于概率分布的统计方法,更真实地反映工艺波动的影响,进行电路优化与良率预测。

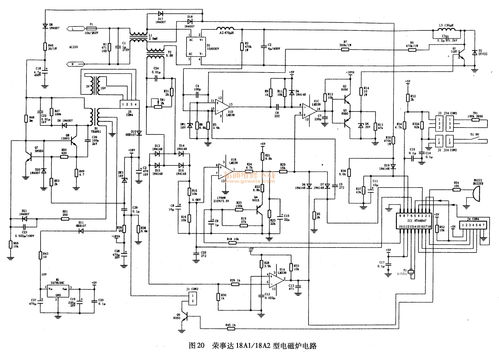

- 可变性感知的综合与布局布线:电子设计自动化(EDA)工具在逻辑综合和物理实现阶段,必须将工艺参数的空间相关性、随机性作为优化约束,生成对波动不敏感且良率更高的电路结构与版图。

- 可靠性建模与寿命预测:建立精确的器件与互连线老化、失效物理模型,并将其集成到标准设计流程中,实现电路级和系统级的寿命仿真与预测。

- 自适应与容错系统设计:设计具备动态电压频率调节(DVFS)、错误检测与纠正(ECC)、冗余逻辑单元等功能的电路与系统架构,使其能够实时感知自身状态并调整工作模式,容忍一定程度的性能退化或瞬时故障。

- 设计-工艺协同优化(DTCO):打破设计与工艺研发的壁垒,在早期阶段就共同探索新的器件结构、互连方案和设计规则,从源头上协同提升性能、密度、成功率和可靠性。

四、未来展望

成功率和可靠性驱动的设计方法学正从先进的数字电路向模拟/射频电路、存储器和三维集成电路(3D-IC)等领域扩展。随着人工智能/机器学习技术的融入,利用大数据分析进行更精准的模型构建、快速的设计空间探索和智能化的可靠性管理,将成为下一代方法学的重要特征。面向量子计算、神经形态计算等新兴计算范式,构建与之相适应的可靠设计方法学也将是未来的前沿方向。

###

在纳米尺度集成电路设计中,将成功率和可靠性置于方法论的中心,已从一种前瞻性理念转变为紧迫的工程实践需求。它要求设计者、EDA工具开发商和晶圆代工厂紧密协作,构建一个覆盖设计、制造、测试、运维全周期的闭环系统。唯有如此,才能持续推动摩尔定律向前演进,为信息社会提供坚实、可信的硬件基石。